Marcel Vinícius Medeiros Oliveira Jim Woodcock (Eds.)

# Formal Methods: Foundations and Applications

12th Brazilian Symposium on Formal Methods, SBMF 2009 Gramado, Brazil, August 2009 Revised Selected Papers

# Lecture Notes in Computer Science

5902

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

TU Dortmund University, Germany

Madhu Sudan

Microsoft Research, Cambridge, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Marcel Vinícius Medeiros Oliveira Jim Woodcock (Eds.)

# Formal Methods: Foundations and Applications

12th Brazilian Symposium on Formal Methods, SBMF 2009 Gramado, Brazil, August 19-21, 2009 Revised Selected Papers

#### Volume Editors

Marcel Vinícius Medeiros Oliveira Universidade Federal do Rio Grande do Norte Departamento de Informática e Matemática Aplicada Campus Universitário, Lagoa Nova, 59078-900 Natal, RN, Brazil E-mail: marcel@dimap.ufrn.br

Jim Woodcock University of York Department of Computer Science Heslington, York YO1 7BZ, UK E-mail: jim@cs.york.ac.uk

Library of Congress Control Number: 2009938928

CR Subject Classification (1998): D.2.4, D.2, F.3, D.3, D.1, K.6, F.4

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-642-10451-7 Springer Berlin Heidelberg New York ISBN-13 978-3-642-10451-0 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

springer.com

© Springer-Verlag Berlin Heidelberg 2009 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12793839 06/3180 5 4 3 2 1 0

#### Preface

This volume contains the papers presented at SBMF 2009: the Brazilian Symposium on Formal Methods, held during August 19–21, 2009 in Gramado, Rio Grande do Sul, Brazil. The SBMF programme included three invited talks given by Leonardo de Moura (Microsoft Research), Sebastian Uchitel (University of Buenos Aires and Imperial College London), and Daniel Kröning (University of Oxford).

The symposium was accompanied by two short courses:

- Introduction to Software Testing, given by Márcio Eduardo Delamaro (University of São Paulo)

- Formal Models for Automatic Test Case Generation, given by Patrícia Machado and Wilkerson Andrade (Federal University of Campina Grande)

This year, the SBMF symposium had a special section on the Grand Challenge in Verified Software, inspired by recent advances in theory and tool support. Work on the grand challenge started with the creation of a Verified Software Repository with two principal aims:

- To collect a set of verified software components

- To conduct a series of industrial-scale verification experiments with theoretical significance and impact on tool-support

This special session on the grand challenge was dedicated to two pilot projects currently underway:

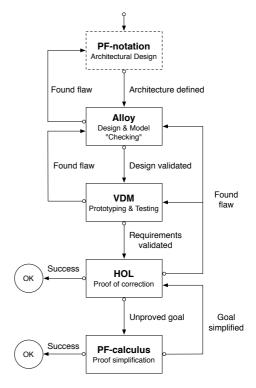

- The Flash File Store. The challenge is to verify the correctness of a fault-tolerant, POSIX-compliant file store implemented on flash memory. Verification issues include dependability guarantees as well as software correctness. Levels of abstraction include requirements specification, software design, executable code, device drivers, and flash translation layers. The challenge was inspired by the requirements for forthcoming NASA space missions.

- FreeRTOS. The challenge is to verify the correctness of an open source real-time mini-kernel. FreeRTOS is designed for real-time performance with limited resources, and is accessible, efficient, and popular: it runs on 17 different architectures and is very widely used in many applications. There are over 5,000 downloads per month from SourceForge, making it the repository's 250th most downloaded code (out of 170,000 codes). FreeRTOS presents a significant verification challenge, in spite of it containing less than 2,500 lines of pointer-rich code.

Attendance at the session gave speakers and participants an opportunity to discuss the state of the art in software verification and to discuss open problems in need of solutions. In particular, it helped to contribute to an open agenda of

research actions for the grand challenge. The papers in the session are of interest to theoreticians, tool builders, tool users, and industrial practitioners.

SBMF was co-located with SAST 2009, the Brazilian Workshop on Systematic and Automated Software Testing. There was a joint technical session on formal aspects of testing, and a joint panel on Academic and Industrial Research Directions in Software Verification.

SBMF was organized by the Instituto de Informática at the Federal University of Rio Grande do Sul (UFRGS) under the auspices of the Brazilian Computer Society (SBC). It was sponsored by the following organizations:

- CNPq, the Brazilian Scientific and Technological Research Council

- CAPES, the Brazilian Higher Education Funding Council

- Banrisul, the Rio Grande do Sul state bank

- The Governor of the State of Rio Grande do Sul

- Microsoft Research

- The Federal University of Rio Grande do Norte (UFRN)

- The University of York

The deliberations of the Programme Committee and the preparation of these proceedings were handled by EasyChair, which made our lives much easier.

September 2009

Marcel Vinícius Medeiros Oliveira James Charles Paul Woodcock

# Conference Organization

# **Programme Chairs**

Marcel Oliveira and Jim Woodcock

# Programme Committee

Aline Andrade David Aspinall Luis Barbosa Roberto Bigonha Michael Butler Andrew Butterfield Ana Cavalcanti Andrea Corradini Jim Davies David Déharbe Ewen Denney Clare Dixon Adolfo Duran Jorge Figueiredo Leo Freitas Rohit Ghevi Rolf Hennicker Juliano Ivoda Moonzoo Kim

Luis Lamb Gerald Lüttgen Patrícia Machado Ana Melo

Ana Meio

Anamaria Moreira

Álvaro Moreira

Arnaldo Moura

Alexandre Mota

David Naumann

Daltro Nunes

José Nuno Oliveira

Alberto Pardo

Alexandre Petrenko

Leila Ribeiro

Augusto Sampaio

Leila Silva

Adenilso Simão

Willem Visser

Heike Wehrheim

# Steering Committee

Ana C. V. de Melo (USP) Jim Woodcock (University of York) Leila Ribeiro (UFRGS) Marcel Oliveira (UFRN) Patrícia Machado (UFCG)

# Organizing Committee

Álvaro Freitas Moreira (Chair; UFRGS) Cláudio Fuzitaki (UFRGS)

#### VIII Organization

Fabiane Cristine Dillenburg (UFRGS) Germano Caumo (UFRGS) Luciana Foss (UFRGS) Lucio Mauro Duarte (UFRGS) Olinto E. David de Oliveira (UFRGS)

# **Table of Contents**

| Speeding Up Simulation of SystemC Using Model Checking  Nicolas Blanc and Daniel Kroening                                                                        | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Partial Behaviour Modelling: Foundations for Incremental and Iterative Model-Based Software Engineering                                                          | 17  |

| Satisfiability Modulo Theories: An Appetizer                                                                                                                     | 23  |

| Interruption Testing of Reactive Systems                                                                                                                         | 37  |

| Test Case Generation of Embedded Real-Time Systems with Interruptions for FreeRTOS                                                                               | 54  |

| Concurrent Models of Flash Memory Device Behaviour                                                                                                               | 70  |

| Corecursive Algebras: A Study of General Structured Corecursion Venanzio Capretta, Tarmo Uustalu, and Varmo Vene                                                 | 84  |

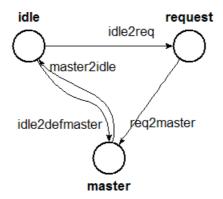

| Formalizing FreeRTOS: First Steps                                                                                                                                | 101 |

| A Mechanized Strategy for Safe Abstraction of CSP Specifications                                                                                                 | 118 |

| Applying Event and Machine Decomposition to a Flash-Based Filestore in Event-B                                                                                   | 134 |

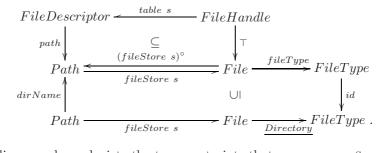

| An Integrated Formal Methods Tool-Chain and Its Application to Verifying a File System Model                                                                     | 153 |

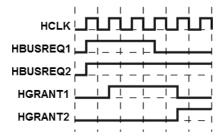

| Towards Safe Design of Synchronous Bus Protocols in Event-B Ricardo Bedin França, Leandro Buss Becker, Jean-Paul Bodeveix, Jean-Marie Farines, and Mamoun Filali | 170 |

| Mechanising Data-Types for Kernel Design in Z                                                                                                                    | 186 |

# X Table of Contents

| A Complete Set of Object Modeling Laws for Alloy                                                                             | 204 |

|------------------------------------------------------------------------------------------------------------------------------|-----|

| Undecidability Results for Distributed Probabilistic Systems                                                                 | 220 |

| Formalisation and Analysis of Objects as CSP Processes                                                                       | 236 |

| Concolic Testing of the Multi-sector Read Operation for Flash Memory File System                                             | 251 |

| Low-Level Code Verification Based on CSP Models                                                                              | 266 |

| Formal Modelling of a Microcontroller Instruction Set in B Valério Medeiros Jr. and David Déharbe                            | 282 |

| Defining Behaviours by Quasi-finality                                                                                        | 290 |

| Verifying Compiled File System Code                                                                                          | 306 |

| Reasoning about General Quantum Programs over Mixed States Juliana Kaizer Vizzotto, Giovani Rubert Librelotto, and Amr Sabry | 321 |

| A Simple and General Theoretical Account for Abstract Types                                                                  | 336 |

| Author Index                                                                                                                 | 351 |

# Speeding Up Simulation of SystemC Using Model Checking\*

Nicolas Blanc<sup>1</sup> and Daniel Kroening<sup>2</sup>

ETH Zurich, Switzerland

Oxford University, Computing Laboratory, UK

Abstract. SystemC is a system-level modeling language that offers a wide range of features to describe concurrent systems. The SystemC standard permits simulators to implement a deterministic thread scheduling policy, which often hides concurrency-related design flaws. We present a novel compiler for SystemC that integrates a formal race analysis based on Model Checking techniques. The key insight to make the formal analysis scalable is to apply the Model Checker only to small partitions of the model. Our compiler produces a simulator that uses the race analysis information at runtime to perform partial-order reduction, thereby eliminating context switches that do not affect the result of the simulation. Experimental results show simulation speedups of one order of magnitude and better.

#### 1 Introduction

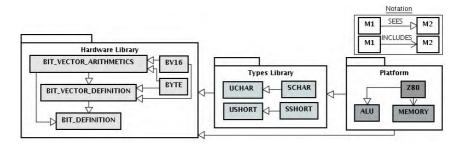

Time-to-market requirements have rushed the Electronic Design Automation (EDA) industry towards design paradigms that require a very high level of abstraction. This high level of abstraction can shorten the design time by enabling the creation of fast executable verification models. This way, bugs in the design can be discovered early in the design process. As part of this paradigm, an abundance of C-like system design languages has emerged. A key feature is joint modeling of both the hardware and software component of a system using a language that is well-known to engineers. A promising candidate for an industry standard is SystemC.

SystemC offers a wide range of language features such as hierarchical design by means of a hierarchy of modules, arbitrary-width bit-vector types, and concurrency with related synchronization mechanisms. SystemC permits different levels of abstraction, from a very high-level specification with big-step transactions down to the gate level. The execution model of SystemC is driven by *events*, which start or resume processes. In addition to communication via shared variables, processes can exchange information through predefined communication channels such as signals and FIFOs.

<sup>\*</sup> This paper is an extended version of a conference paper that appeared at ICCAD 2008 [1]. This research is supported by ETH research grant TH-21/05-1 and by the Semiconductor Research Corporation (SRC) under contract no. 2006-TJ-1539.

Technically, SystemC programs rely on a C++ template library. SystemC modules are therefore plain C++ classes, which are compiled and then linked to a runtime scheduler. This provides a simple yet efficient way to simulate the behavior of the system. Methods of a module may be designated as threads or processes. Interleaving between those threads is performed at pre-determined program locations, e.g., at the end of a thread or when the wait() method is called. When multiple threads are ready for execution, the ordering of the threads is nondeterministic. Nevertheless, the SystemC standard allows simulators to adopt a deterministic scheduling policy. Consequently, simulators can avoid problematic schedules, which often prevents the discovery of concurrency-related design flaws.

When describing synchronous circuits at the register transfer level, system designers can prevent races by restricting inter-process communication to deterministic communication channels such as *sc\_signals*. However, the elimination of races from the high-level model is often not desirable: In practice, system designers often use constructs that yield races in order to model nondeterministic choices implicit in the design. In particular, models containing standard transaction-level modeling (TLM) interfaces are frequently subject to race phenomena. TLM designs usually consist of agents sharing communication resources and competing for access to them. An example is a FIFO with two clock domains: the races model the different orderings of the clock events that can arise.

Contribution. Due to the combinatorial explosion of process interleavings, testing methods for concurrent software alone are unlikely to detect bugs that depend on subtle interleavings. Therefore, we propose to employ formal methods to statically pre-compute thread-dependency relations and predicates that predict race conditions, and to use this information subsequently during the simulation run to prune the exploration of concurrent behaviors. There are two possible ways of exploiting the information:

- 1. In general, proving or refuting process independence requires precise static analysis. From a designer perspective, the statically computed dependency relations between the threads provide key insights into potential races.

- 2. The statically computed race conditions improve the performance of partial order reduction, which results in a greatly reduced number of interleavings. The remaining interleavings can then be explored exhaustively, which is a valuable validation aid.

We have implemented this technique in Scoot [2], a novel research compiler for SystemC. The static computation of the race conditions relies on a Model Checker. The technique we propose is independent of the specific formal engine. We have performed our experiments using SATABS [3], a SAT-based Model Checker implementing predicate abstraction, and CBMC, a SAT-based bounded Model Checker. Our experimental results indicate that strong race conditions can be computed statically at reasonable cost, and result in a simulation speedup of a factor of ten or better.

#### Related Work

Concurrent threads with nondeterministic interleaving semantics may give rise to races. A data race is a special kind of race that occurs in a multi-threaded application when several processes enter a critical section simultaneously [4]. Flanagan and Freud use a formal type system to detect race-condition patterns in Java [5]. Eraser is a dynamic data-race detector for concurrent applications [6]. It uses binary rewriting techniques to monitor shared variables and to find failures of the locking discipline at runtime. Other tools, such as RacerX [7] and Chord [8], rely on classic pointer-analysis techniques to statically detect data races. Data races can also occur in SystemC if processes call synchronization routines while holding shared resources.

Model Checkers are frequently applied to the verification of concurrent applications, and SystemC programs are an instance; see [9] for a survey on software Model Checking. Vardi identifies formal verification of SystemC models as a research challenge [10]. Prior applications of formal analysis to SystemC or similar languages are indeed limited. We therefore briefly survey recent advances in the application of such tools to system-level software. DDVerify is a tool for the verification of Linux device drivers [11]. It places the modules into a concurrent environment and relies on SATABS for the verification. KISS is a tool for the static analysis of multi-threaded programs written in C [12]. It reduces the verification of a concurrent application to the verification of a sequential program with only one stack by bounding the number of context switches. The reduction never produces false alarms, but is only complete up to a specific number of context switches. KISS uses SLAM [13], a Model Checker based on Predicate Abstraction [14,15], to verify the sequential model.

Verisoft is a popular tool for the systematic exploration of the state space of concurrent applications [16] and could, in principle, be adapted to System C. The execution of processes is synchronized at visible operations, which are system calls monitored by the environment. Verisoft systematically explores the schedules of the processes without storing information about the visited states. Such a method is, therefore, referred to as a state-less search. Verisoft's support for partial-order reduction relies exclusively on dynamic information to achieve the reduction. In a recent paper, Sen et al. propose a modified System C-Scheduler that aims to detect design flaws that depend on specific schedules [17]. The scheduler relies on dynamic information only, i.e., the information has to be computed during simulation, which incurs an additional run-time overhead. In contrast, Scoot statically computes the conditions that guarantee independence of the transitions. The analysis is very precise, as it is based on a Model Checker, and Scoot is therefore able to detect opportunities for partial-order reduction with little overhead during simulation.

Flanagan and Godefroid describe a state-less search technique with support for partial-order reduction [18]. Their method runs a program up to completion, recording information about inter-process communication. Subsequently, the trace is analyzed to detect alternative transitions that might lead to different behaviors. Alternative schedules are built using *happens-before* information,

which defines a partial-order relation on all events of all processes in the system [19]. The procedure explores alternative schedules until all relevant traces are discovered. Helmstetter et al. present a partial-order reduction technique for SystemC [20]. Their approach relies on dynamic information and is similar to Flanagan and Godefroid's technique [18]. Their simulator starts with a random execution, and observes visible operations to detect dependency between the processes and to fork the execution. Our technique performs a powerful analysis statically that is able to discover partial-order reduction opportunities not detectable using only dynamic information.

Kundu et al. propose to compute read/write dependencies between SystemC processes using a path-sensitive static analysis [21]. At runtime, their simulator starts with a random execution and detects dependent transitions using static information. The novelty of our approach is to combine conventional static analysis with Model Checking to compute sufficient conditions over the global variables of the SystemC model that guarantee commutativity of the processes.

Wang et al. introduce the notion of guarded independence for pairs of transitions [22]. Their idea is to compute a condition (or guard) that holds in the states where two specific transitions are independent. Our contribution in this context is to compute these conditions for SystemC using a Model Checker.

# 2 Partial-Order Reduction for SystemC

In this section, we provide a brief introduction to the concurrency model of SystemC and describe the challenges of applying partial-order reduction in the context of SystemC.

# 2.1 An Overview of the Concurrency Model of SystemC

The dominating concurrency model for software permits asynchronous interleavings between threads, that is, running processes are preempted. SystemC is different as it is mainly designed for modeling synchronous systems. Its scheduler has a *co-operative multitasking* semantics, meaning that the execution of processes is serialized by explicit calls to a wait() method, and that threads are not preempted.

The SystemC scheduler tracks simulation time and *delta cycles*. The simulation time is a positive integer value (the clock). Delta cycles are used to stabilize the state of the system. A delta cycle consists of three phases: *evaluate*, *update*, and *notify*.

1. The evaluation phase selects a process from the set of runnable processes and triggers or resumes its execution. The process runs immediately up to the point where it returns or invokes the *wait* function. The evaluation phase is iterated until the set of runnable processes is empty. The SystemC standard allows simulators to choose any runnable process, as long as the policy is consistent between runs.

#### **Program 1.** A SystemC module with a race condition

```

SC_MODULE(m) {

sc_clock clk; int pressure;

void guard() {

if(pressure == PMAX) pressure = PMAX-1;

}

void increment() { pressure++; }

SC_CTOR(m) {

SC_METHOD(guard); sensitive << clk;

SC_METHOD(increment); sensitive << clk;

}

};</pre>

```

- 2. In order to simulate synchronous executions, processes can delay change-of-state effects by scheduling *update requests*. After the evaluation phase terminates, the kernel executes any pending update request. This is called the *update phase*. Signal assignments are typically implemented using the update mechanism. Therefore, signals keep their value for an entire evaluation phase.

- 3. Finally, during the *delta-notification phase*, the scheduler determines which processes are sensitive to events that have occurred, and adds all such processes to the set of runnable processes.

The scheduler executes delta cycles until the set of runnable processes is empty at the beginning of the evaluation phase. Subsequently, it updates the simulation time and notifies processes waiting for the time event.

#### 2.2 A Motivating Example

Program 1 serves as running example and illustrates the need for a combination of Model Checking and partial-order reduction. The module m declares two processes guard and increment. The process guard watches the value of shared variable pressure, which shall not exceed the value PMAX and is incremented by process increment. Both processes are sensitive to the clock signal clk. The semantics of the SystemC scheduler guarantees that a method process is executed without interruption up to the point where it returns. Thus, the scheduler has to choose either the scheduling sequence (guard; increment) or (increment; guard) each time the clock is updated. Consequently, the pressure can exceed the limit if its value reaches PMAX and the process increment is triggered before guard. It is clear that the number of traces grows exponentially with the number of clock cycles. As a result, systematic exploration of all interleavings rapidly becomes unmanageable, and the bad behavior might go unnoticed.

A conventional static analysis can discover that *guard* reads the pressure and that *increment* modifies the pressure, concluding that the processes are indeed

dependent and that all interleavings must be explored. Similarly, a conventional dynamic analysis would always detect a read/write dependency between *guard* and *increment*, forcing the simulator to execute all schedules. However, such analyses fail to detect that *guard* and *increment* are commutative in most cases. Our tool uses a Model Checker to compute the weakest predicate over the prestate variables that guarantees the absence of races between the processes. In this example, it is easy to see that the execution of *increment* and *guard* is commutative if and only if

$$pressure \neq PMAX - 1 \land pressure \neq PMAX$$

holds. Scoot generates a simulator for the systematic exploration of the state space that checks this condition at runtime to avoid exploring redundant schedules.

#### 2.3 Background on Partial-Order Reduction

Partial-order reduction is a technique to explore the state space of concurrent systems in a way that preserves the soundness of the verification result [23,24,25]. The key idea is to exploit commutativity of transitions to obtain a subset of all possible interleavings from a state such that the reduced state graph retains a representative behavior for each behavior that is removed. Scoot uses partial-order reduction to generate a simulator that explores only necessary interleavings. We briefly survey the standard definitions from the literature in this section [25].

The literature distinguishes between partial-order reduction based on *persistent sets* and reduction based on *sleep sets*. The two approaches are orthogonal and achieve better results when combined. Both techniques compute a subset of the runnable transitions for each visited state and restrict future exploration to transitions in this set.

We denote the set of states and the set of processes of a SystemC model by S and  $\theta$ , respectively. We denote the set of enabled (runnable) processes (transitions) in a state s by Enabled(s), i.e., Enabled is a mapping from S to  $\mathscr{P}(\theta)$ . Processes are relations between states. We write  $s \xrightarrow{\alpha} t$  to denote that the state changes from s to t by executing process t.

**Definition 1.** [22] Two transitions  $\alpha$  and  $\beta$  are guarded independent with respect to a guard  $\phi \subseteq S$  if and only if for all  $s \in \phi$  and  $t \in S$  the following hold:

1.

$$\alpha \in Enabled(s) \land s \xrightarrow{\alpha} t \Rightarrow$$

$\beta \in Enabled(s) \Leftrightarrow \beta \in Enabled(t)$

2.  $\beta \in Enabled(s) \land s \xrightarrow{\beta} t \Rightarrow$

$\alpha \in Enabled(s) \Leftrightarrow \alpha \in Enabled(t)$

3.  $\alpha, \beta \in Enabled(s) \Rightarrow$

$\langle s, t \rangle \in \alpha \circ \beta \Leftrightarrow \langle s, t \rangle \in \beta \circ \alpha$

The first two conditions guarantee that  $\alpha$  and  $\beta$  cannot disable nor enable each other in s, while the third condition requires  $\alpha$  and  $\beta$  to be commutative in s.

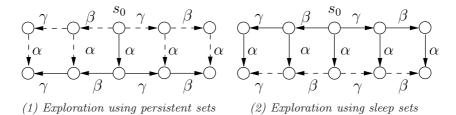

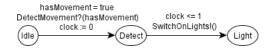

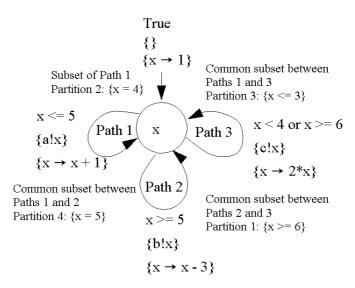

**Fig. 1.** Example of partial-order reduction using persistent sets (1) and sleep sets (2). The reduced state graph contains only the transitions depicted with solid lines.

SCOOT uses Model Checking to compute the condition  $\phi$ . Transitions  $\alpha$  and  $\beta$  are independent in s if and only if  $\alpha, \beta$  are guarded independent with respect to the guard  $\{s\}$  [25].

**Definition 2.** [25] Let  $D \subseteq \theta \times \theta$  be a symmetric and reflexive relation over the transitions of the system. The relation D is a valid dependency relation for  $\theta$  if and only if  $(\alpha, \beta) \notin D$  implies that  $\alpha, \beta$  are independent in all reachable states.

Similar to [21], SCOOT uses a data-flow analysis in order to compute an overapproximating dependency relation.

**Definition 3.** [25] Let  $(S, S_0, \theta)$  be a transition system, and  $s_0 \in S$  denote one of its states. A set of transitions  $T \subset Enabled(s_0)$  is persistent in  $s_0$  if and only if for all  $\beta \in T$  and all sub-traces  $s_0 \stackrel{\alpha_0}{\to} s_1 \stackrel{\alpha_1}{\to} s_2...s_n \stackrel{\alpha_n}{\to} s_{n+1}$  obtained from transitions  $\alpha_i \notin T$ ,  $\beta$  and  $\alpha_i$  are independent in  $s_i$ .

The Definition 3 is, thus, concerned about what can happen in the *future*. The persistent-set technique computes a persistent set of runnable transitions in each visited state and restricts the exploration to transitions in this set only. Persistent sets are typically computed using information from a preliminary static analysis.

Figure 1.1 illustrates the effects of the persistent-set technique. In state  $s_0$ , the exploration uses the persistent set  $T = \{\alpha\}$  to avoid visiting some of the states. In contrast, the sleep-set technique maintains a set of runnable transitions that can be skipped during the exploration (the sleep set). The method is concerned with branching information from the past. Figure 1.2 shows a typical exploration using sleep sets. Unlike the previous approach, the sleep-set technique only reduces the number of explored transitions and has no effect on the number of explored states. The exploration backtracks early when the sleep set contains all runnable transitions.

# 3 Implementation

#### 3.1 Overview of Scoot

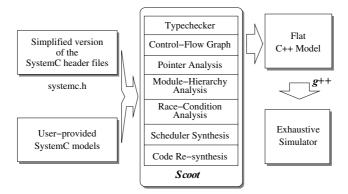

Figure 2 shows an overview of Scoot. We use an in-house C++ front-end to translate the SystemC source files into a control flow graph (CFG). The

Fig. 2. Overview of Scoot

front-end of Scoot accepts a large subset of C++ including inheritance, overloading, virtual functions, and many forms of templates.

SCOOT abstracts implementation details of the SystemC library by using simplified header files that declare only relevant aspects of the API and omit the actual implementation. Subsequently, SCOOT uses static analysis techniques to discover the module hierarchy, the sensitivity list of processes, and the port bindings. The next step is the computation of race conditions for each pair of processes, which is explained in Sec. 3.3. SCOOT then generates the code for the exhaustive simulator. Finally, SCOOT translates the CFG back to a flat C++ program, which no longer requires the SystemC library. We use g++ to compile the C++ file and to obtain an executable simulator.

We forbid dynamic creation of processes and dynamic modifications of sensitivity lists (next\_trigger functions). The support for SystemC currently comprises static creation of processes, static sensitivity lists, waiting using sensitivity lists, waiting for a specific event, waiting for a certain amount of time, immediate notification, delta notification, time notification, and communication channels such as sc\_signals, sc\_fifos, and tlm\_fifos. We have a broad support for the general features of C++; e.g., our support for STL container classes is described in [26].

#### 3.2 A Scheduler with Partial-Order Reduction

Algorithm 1 is SCOOT's implementation of the evaluation phase. In contrast to the related work, *evaluation\_phase* schedules runnable processes using information *statically* collected to reduce the number of interleavings explored. We are not aware of tools that compute equally strong conditions statically.

The evaluation phase terminates once the set of runnable processes is empty. The algorithm performs partial-order reduction using persistent sets and sleep sets, and is a variation of techniques presented by Godefroid [25]. On line 3, the procedure calls the function runnable() to check if the set of runnable processes is empty before proceeding to the next iteration.

**Algorithm 1.** Evaluation Phase: the commutativity condition checked by commutative  $(p_i, p_j)$  is a predicate over states computed statically at compile-time

```

void evaluation_phase()

Set sleeps := \emptyset;

while (runnable() \neq \emptyset) do

persistents := get_pers();

awakes := persistents \ sleeps;

if (awakes = \emptyset) then exit (0);

6

Map next_sleeps; // Process -> Set

for all (Process p_i \in \text{awakes}) do

for all (Process p_j \in \text{sleep}) do

if (commutative (p_i, p_i))

10

next\_sleeps[p_i] := next\_sleeps[p_i] \cup \{p_i\};

end for

12

sleep := sleep \cup \{p_i\};

end for

Process p := nondet\_select(awakes);

16

sleeps := next\_sleeps[p];

end while

18

```

At simulation time, the scheduler calls qet\_pers to compute the set persistents of persistent processes. The subsequent part of the algorithm uses the set sleeps, declared outside the main loop on line 2, to perform partial-order reduction. On line 5, the set awakes consists of the persistent processes not in sleeps. If the set of awaken processes is empty (line 6), then other traces are covering all subsequent behaviors, and therefore, the simulator stops the execution. Otherwise, the scheduler computes the sleep sets for the next iteration using the map next\_sleeps, which maps processes to a set of processes (lines 7–14). One line 10, the call to commutative returns true if the processes  $p_i$  and  $p_j$  are commutative in the current state. The scheduler reduces the computation of conditional independence to the computation of commutativity conditions by considering that all the processes are always enabled – if  $\rho \notin Enabled(s)$ , then this is interpreted as  $s \xrightarrow{\rho} s$ . This way, two processes are independent in the current state if and only if they are commutative in this state. Scoot relies on Model Checking to compute a conservative condition that guarantees commutativity of the processes in the current state; the details of this pre-computation are presented in the following subsection. In contrast, traditional approaches need to rely on either executing the processes to determine which transitions are independent in the current state, which adds overhead, or on an imprecise data-flow analysis.

Finally, in lines 15–17, the scheduling algorithm nondeterministically runs a process from *awakes* and computes the sleep set of the next iteration.

#### 3.3 Computing the Process Commutativity Conditions

We present an iterative technique to compute the commutativity condition for a given pair of processes  $p_1$  and  $p_2$  based on formal analysis. The condition is checked during simulation by Alg. 1. In general, SystemC processes need not terminate, and thus computing the strongest possible commutativity condition for a given pair of processes  $p_1$  and  $p_2$  is undecidable. We compute a conservative approximation by applying a Model Checker to the harness given as Program 2.

**Program 2.** Harness for the analysis of race conditions for a given pair of processes p1 and p2. The pre-condition  $\phi$  is true initially, and is then iteratively strengthened

```

assume (\phi);

s_0 := \text{current\_state};

p_1(); p_2();

s_{1,2} := \text{current\_state};

\text{current\_state} := s_0;

s_2(); p_1();

s_{2,1} := \text{current\_state};

assert (s_{1,2} \neq s_{2,1});

```

The basic idea of the harness is to run  $p_1()$ ;  $p_2()$ , and compare the result with the result of running  $p_2()$ ;  $p_1()$  on the same initial state. The harness operates as follows: Initially,  $\phi$  is set to *true*. The assume statement in the first line restricts the search to states that satisfy  $\phi$ . Then the values of the visible variables are stored in  $s_0$ , the pair of processes  $p_1()$ ;  $p_2()$  is run, and the state is stored in  $s_{1,2}$ . The state is restored to  $s_0$ , and  $p_2()$ ;  $p_1()$  is run. The state is stored in  $s_{2,1}$ .

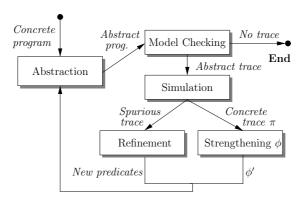

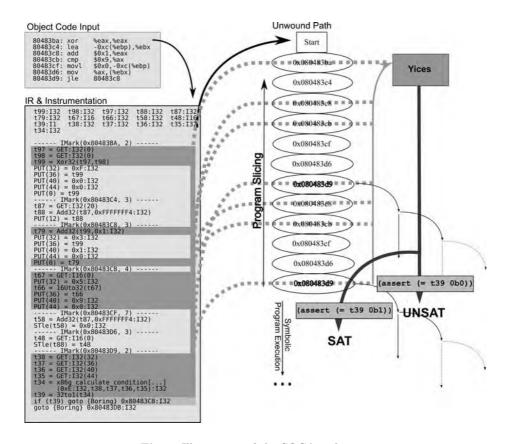

SCOOT passes the harness to a Model Checker to check the reachability of the last line, which is modeled by means of an assertion. If the Model Checker returns a counterexample, we have a trace  $\pi$  with an initial state satisfying the initial condition  $\phi$ , passing through both processes, and ending in a state that violates the assertion. The path therefore begins in a state in which the two processes are commutative. SCOOT then computes the weakest precondition of  $s_{1,2} = s_{2,1}$  alongside that path. Let  $P_{\pi}$  denote this condition. The executions of  $p_1(); p_2()$  and  $p_2(); p_1()$  from a state s terminate and yield an equal state if s satisfies  $P_{\pi}$ . Consequently,  $P_{\pi}$  is an under-approximation of the commutativity condition for  $p_1$  and  $p_2$ . At this point, SCOOT strengthens  $\phi$  using  $\neg P_{\pi}$ , yielding  $\phi'$ . This removes the trace  $\pi$  and any trace similar to  $\pi$  that goes through the same control locations. SCOOT iterates this process until the Model Checker stops reporting counterexamples. At this point, the predicate  $P = \bigvee_{\pi} P_{\pi}$  represents the weakest condition such that the executions of  $p_1(); p_2()$  and  $p_2(); p_1()$  terminate and that  $p_1$  and  $p_2$  are commutative.

In practice, we observe that the number of facts that SCOOT tracks during the computation of the weakest precondition of  $s_{1,2} = s_{2,1}$  may explode. Therefore, instead of comparing the entire state vectors  $s_{1,2}$  and  $s_{2,1}$ , we restrict the

comparison to the variables written by the processes. This set is determined by means of a standard data-flow analysis.

In the following, we elaborate on our integration of the strengthening loop into SATABS, a Model Checker based on predicate abstraction. Note that our approach is independent of the particular Model Checking engine. The general idea can be extended in different directions. As an example, we can adapt the strengthening loop to operate on infinite traces using a Model Checker for liveness properties such as Terminator [27], or we can replace the Model Checker with a testing engine to discover terminating traces at the cost of code-coverage guarantees.

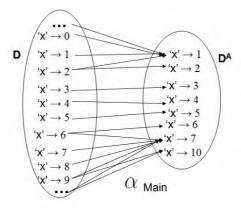

Strengthening Using Predicate Abstraction. Predicate Abstraction is a technique that abstracts a transition system by mapping sets of concrete states to a new, smaller abstract state space in a way that conserves the relevant behaviors of the system [14,15]. Each predicate in the abstract model is represented by a Boolean variable, while the original variables are removed. The abstract program is created using existential abstraction, which is a conservative abstraction for reachability properties. If the property holds on the abstract model, it also holds on the original program. In case a trace in the abstract model violates the property, the feasibility of the counterexample must be tested in the concrete model. If the counterexample can be simulated on the original program, it is reported to the user. The counterexample is called *spurious* if it does not correspond to a concrete trace. In that case, a refinement procedure adds new predicates in a way that removes the spurious trace. This is automated by Counterexample Guided Abstraction Refinement (CEGAR) [28] and promoted by the Model Checker Slam [13]. Predicate abstraction has been applied to SpecC [29] and SystemC [30]. Figure 3 shows the integration of our technique into SATABS. After strengthening, SATABS retains the abstract model obtained during previous iterations.

Fig. 3. Iterative computation of the process commutativity condition using predicate abstraction

# 4 Experimental Evaluation

In this section, we evaluate the benefits of integrating our partial-order reduction into a simulator that examines all schedules exhaustively using a backtracking search. The experiments that we present are difficult instances. Commutativity of processes depends on control flow and data, and the computation of the condition is susceptible to the state-space explosion problem. We obtained our results on a 3GHz Linux machine. We make the benchmarks and the tool available for experimentation by other researchers at <a href="https://www.cprover.org/scoot/">www.cprover.org/scoot/</a>.

#### 4.1 The Running Example

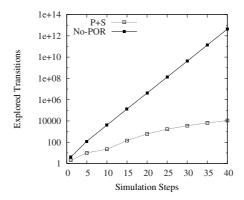

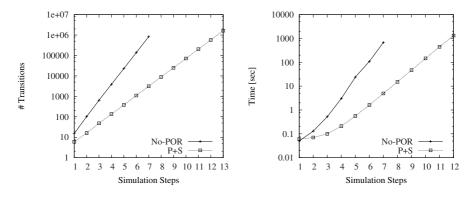

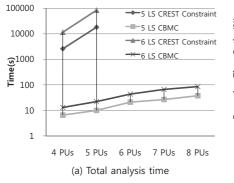

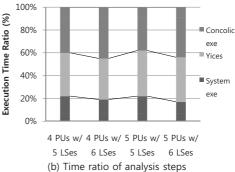

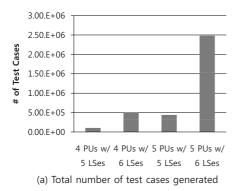

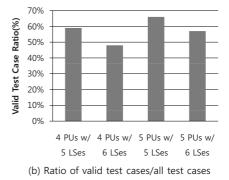

We continue our running example (Program 1). Figure 4 depicts the number of explored transitions as a function of the number of simulation steps using persistent and sleep sets (P+S) and without partial-order reduction (No-POR). We set PMAX to 10. Our simulator performs a state-less search, that is, the simulator replays transitions to backtrack. Those transitions are counted only once. With this technique, the number of transitions explored during simulation grows quadratically with the number of steps, whereas without partial-order reduction, the curve grows exponentially. As mentioned before, a conventional dynamic analysis would always detect a read/write dependency between the two processes, forcing the simulator to explore all schedules.

Fig. 4. Number of transitions explored at runtime as a function of the number of simulation steps

#### 4.2 State Machines

We use two different benchmarks to evaluate the benefit of statically computed race conditions. The first benchmark (B1) consists of a synchronous model with three dependent processes. One process plays the role of a server waiting for requests, while the other two compete for access to the service. Program 3 contains the skeleton of the benchmark. When triggered, the clients and the server execute

#### Program 3. Skeleton of Benchmark B1

```

bool locked; int op;

void process_client() {

if(!locked){ op=get_pid(); locked=true;}

void process_server(){

switch(state) {

...

case Idle: {switch(op) {...} break;}

case End: {state = Idle; locked = false;}

}

```

functions process\_client and process\_server, respectively. The clients communicate with the server via two shared variables op and locked. If locked is set, then the server is busy processing the request op. Otherwise, the clients compete for access to the service. The processes are sensitive to a clock. Figure 5 compares the number of explored transitions, and the total exploration time as a function of the number of simulation steps. We present results without partial-order reduction (No-POR) and using a combination of sleep sets and persistent sets (P+S). The exploration time is limited to thirty minutes (1800 seconds).

The results indicate that partial-order reduction using statically computed commutativity conditions is able to significantly reduce both the number of explored transitions and the exploration time by about two to three orders of magnitude. With partial-order reduction, the simulator can exhaustively cover all the relevant behaviors up to twelve simulation steps in less than thirty minutes, whereas the naive approach already times out after seven simulation steps.

Our second benchmark (B2) consists of two synchronous state machines communicating via shared variables. The model has three interdependent processes,

Fig. 5. Performance effect of static partial-order reduction on B1

Benchmark Pair SATABS [s] CBMC [s] **B**1 0 < 1< 13 В1 1 < 12 B1 3 < 1ТО B20 76 1 B219 5 2 B22 19

**Table 1.** Time to compute the race conditions for each of the process-pairs using SATABS and CBMC. The timeout is set to ten minutes.

which are sensitive to the clock. The state machines are implemented using case switches. On this benchmark, partial-order reduction reduces the simulation time and the number of explored transition by one order of one magnitude.

For each pair of processes, Table 1 shows the time required for the static analysis running SATABS and CBMC. The cost for B1 is negligible using both SATABS and CBMC. The results for B2 indicate that CBMC is faster than SATABS on the second and third pair of processes but times out on the first one, whereas SATABS provides a result within two minutes. Note that the computation of these conditions can be distributed onto multiple machines, as the computation for each pair of processes is independent. Furthermore, the precision of the analysis can be controlled by bounding the number of strengthening iterations, which yields a conservative approximation. Finally, as demonstrated by the experiments, the time required for a full exploration grows exponentially with the number of simulation steps, and therefore, the time spent statically for a precise analysis eventually pays off.

#### 5 Conclusion

We presented SCOOT, a novel compiler for SystemC that integrates static analysis and formal verification techniques in order to improve simulation performance. We invoke a modified software Model Checker on each pair of dependent transitions in order to compute a sufficient condition for commutativity of the transitions. Our technique benefits from the fact that SystemC processes are not preempted, and thus, only few such pairs have to be checked. Note that the Model Checker is never applied to the entire model, but only to pairs of transitions – the static part of the analysis is therefore typically polynomial in the size and number of processes.

SCOOT uses the commutativity condition during simulation in order to eliminate unnecessary interleavings. Our analysis is fully automatic and requires no annotation of the source code by the user. Using Model Checking, our analysis is able to detect reduction opportunities that depend on subtle control-flow properties. The experimental results indicate that our formal race-analysis technique produces valuable information for pruning the state space at runtime.

#### References

- Blanc, N., Kroening, D.: Race analysis for SystemC using model checking. In: Proceedings of ICCAD 2008, pp. 356–363. IEEE, Los Alamitos (2008)

- Blanc, N., Kroening, D., Sharygina, N.: Scoot: A tool for the analysis of SystemC models. In: Ramakrishnan, C.R., Rehof, J. (eds.) TACAS 2008. LNCS, vol. 4963, pp. 467–470. Springer, Heidelberg (2008)

- 3. Clarke, E., Kroening, D., Sharygina, N., Yorav, K.: SATABS: SAT-based predicate abstraction for ANSI-C. In: Halbwachs, N., Zuck, L.D. (eds.) TACAS 2005. LNCS, vol. 3440, pp. 570–574. Springer, Heidelberg (2005)

- 4. Netzer, R.H.B., Miller, B.P.: What are race conditions? Some issues and formalizations. ACM Lett. Program. Lang. Syst. 1, 74–88 (1992)

- 5. Flanagan, C., Freund, S.N.: Type-based race detection for Java. In: Programming language design and implementation (PLDI), pp. 219–232. ACM, New York (2000)

- Savage, S., Burrows, M., Nelson, G., Sobalvarro, P., Anderson, T.: Eraser: A dynamic data race detector for multithreaded programs. ACM Trans. Comput. Syst. 15, 391–411 (1997)

- Engler, D., Ashcraft, K.: RacerX: Effective, static detection of race conditions and deadlocks. In: Operating systems principles (SOSP), pp. 237–252. ACM, New York (2003)

- Naik, M., Aiken, A., Whaley, J.: Effective static race detection for Java. In: Programming language design and implementation (PLDI), pp. 308–319. ACM, New York (2006)

- D'Silva, V., Kroening, D., Weissenbacher, G.: A survey of automated techniques for formal software verification. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD) 27, 1165–1178 (2008)

- 10. Vardi, M.Y.: Formal techniques for SystemC verification. In: Design Automation Conference (DAC), pp. 188–192. ACM, New York (2007)

- Witkowski, T., Blanc, N., Kroening, D., Weissenbacher, G.: Model checking concurrent Linux device drivers. In: Automated software engineering (ASE), pp. 501–504.

ACM, New York (2007)

- Qadeer, S., Wu, D.: KISS: keep it simple and sequential. SIGPLAN Not. 39, 14–24 (2004)

- 13. Ball, T., Rajamani, S.K.: The SLAM project: debugging system software via static analysis. In: POPL 2002: Proceedings of the 29th ACM SIGPLAN-SIGACT symposium on Principles of programming languages, pp. 1–3. ACM, New York (2002)

- Graf, S., Saïdi, H.: Construction of abstract state graphs with PVS. In: Grumberg,

O. (ed.) CAV 1997. LNCS, vol. 1254, pp. 72–83. Springer, Heidelberg (1997)

- 15. Ball, T., Rajamani, S.: Boolean programs: A model and process for software analysis. Technical Report MSR-TR-2000-14, Microsoft Research (2000)

- Godefroid, P.: Software model checking: The VeriSoft approach. Form. Methods Syst. Des. 26, 77–101 (2005)

- Sen, A., Ogale, V., Abadir, M.S.: Predictive runtime verification of multi-processor SoCs in SystemC. In: Design Automation Conference (DAC), pp. 948–953. ACM, New York (2008)

- Flanagan, C., Godefroid, P.: Dynamic partial-order reduction for model checking software. In: Principles of programming languages (POPL), pp. 110–121. ACM, New York (2005)

- 19. Lamport, L.: Time, clocks, and the ordering of events in a distributed system. Commun. ACM 21, 558–565 (1978)

- 20. Helmstetter, C., Maraninchi, F., Maillet-Contoz, L., Moy, M.: Automatic generation of schedulings for improving the test coverage of systems-on-a-chip. In: Formal Methods in Computer Aided Design (FMCAD), pp. 171–178. IEEE Computer Society, Los Alamitos (2006)

- Kundu, S., Ganai, M., Gupta, R.: Partial order reduction for scalable testing of SystemC TLM designs. In: Design Automation Conference (DAC), pp. 936–941.

ACM, New York (2008)

- Wang, C., Yang, Z., Kahlon, V., Gupta, A.: Peephole partial order reduction. In: Ramakrishnan, C.R., Rehof, J. (eds.) TACAS 2008. LNCS, vol. 4963, pp. 382–396. Springer, Heidelberg (2008)

- Peled, D.: All from one, one for all: On model checking using representatives. In: Courcoubetis, C. (ed.) CAV 1993. LNCS, vol. 697, pp. 409–423. Springer, Heidelberg (1993)

- Peled, D.: Combining partial order reductions with on-the-fly model-checking. In: Dill, D.L. (ed.) CAV 1994. LNCS, vol. 818, pp. 377–390. Springer, Heidelberg (1994)

- 25. Godefroid, P.: Partial-Order Methods for the Verification of Concurrent Systems. LNCS. Springer, Heidelberg (1996)

- 26. Blanc, N., Groce, A., Kroening, D.: Verifying C++ with STL containers via predicate abstraction. In: 22nd IEEE International Conference on Automated Software Engineering (ASE), pp. 521–524. IEEE, Los Alamitos (2007)

- Cook, B., Podelski, A., Rybalchenko, A.: Terminator: Beyond safety. In: Ball, T., Jones, R.B. (eds.) CAV 2006. LNCS, vol. 4144, pp. 415–418. Springer, Heidelberg (2006)

- Clarke, E.M., Grumberg, O., Jha, S., Lu, Y., Veith, H.: Counterexample-guided abstraction refinement. In: Emerson, E.A., Sistla, A.P. (eds.) CAV 2000. LNCS, vol. 1855, pp. 154–169. Springer, Heidelberg (2000)

- 29. Clarke, E., Jain, H., Kroening, D.: Verification of SpecC using predicate abstraction. Form. Methods Syst. Des. 30, 5–28 (2007)

- Kroening, D., Sharygina, N.: Formal verification of SystemC by automatic hardware/software partitioning. In: Formal Methods and Models for Co-Design (MEM-OCODE), pp. 101–110. IEEE Computer Society, Los Alamitos (2005)

# Partial Behaviour Modelling: Foundations for Incremental and Iterative Model-Based Software Engineering

Sebastian Uchitel<sup>1,2</sup>

Department of Computing, Imperial College London, 180 Queen's Gate, London, SW7 2RH, UK

Department of Computer Science, FCEN, Universidad de Buenos Aires, Intendente Güiraldes 2160, C1428EGA, Argentina suchitel@dc.uba.ar, s.uchitel@doc.ic.ac.uk

**Abstract.** Rigorous modelling of the intended behaviour of software intensive systems has been shown to be successfull in uncovering requirements and design flaws. However, the impact that behaviour modelling has had among practitioners is limited. The construction of behaviour models remains a difficult and laborious task that requires significant expertise. In addition, traditional approaches to behaviour models require complete descriptions of the system behaviour up to some level of abstraction. This completeness assumption is limiting in the context of software development process best practices which include iterative development, adoption of use-case and scenario-based techniques and viewpoint- or stakeholder-based analysis; practices which require modelling and analysis in the presence of partial information about system behaviour. Our aim is to support the iterative and incremental construction of behaviour models by means of construction, composition and analysis of partial, heterogeneous, yet formal, descriptions of behaviour. In this talk we discuss how modal transitions systems can provide the basis for such support and present some of the model synthesis and composition techniques we have developed.

#### 1 Introduction

Software systems are amenable to analysis through the construction of behaviour models. This corresponds to the traditional engineering approach to construction of complex systems. Models can be studied to increase confidence on the adequacy of the product to be built. The advantage of using behaviour models to describe systems is that they are cheaper to develop than the actual system. Consequently, they can be analysed and mechanically checked for properties in order to detect design errors early in the development process and allow cheaper fixes.

Although behaviour modelling and analysis has been shown to be successful in uncovering subtle requirements and design errors, adoption by practitioners has been slow. Partly, this is due to the complexity of building behavioural models

in the first place – behaviour modelling remains a difficult, labour-intensive task that requires considerable expertise. To address this, a wide range of techniques for supporting automated and semi-automated synthesis of behaviour models have been investigated. In particular, synthesis from scenarios and use cases (e.g., [24,10,3,19]), has been studied extensively.

A current limitation of synthesis approaches is that the models being synthesized, e.g., labeled transition systems (LTSs) [14], are typically assumed to be complete descriptions of the system behaviour. That is, that they completely classify all behaviours with respect to some fixed alphabet as either behaviour that the system-to-be is required to exhibit or behaviour that the system-to-be is prohibited from exhibiting. The required behaviour is decribed by the transitions that appear in the behaviour model. The proscribed behaviour is defined as anything that is not described by the model's transitions. This completeness assumption that usually is attached to behaviour models is problematic if these models is to be built from a scenario based-specifications which is inherently partial as synthesis procedures are left to cope with completing the specification automatically, or the engineer is required to put in more information before any meaningful analysis can be performed. Utlimately, this completeness assumption is limiting in the context of software development process best practices which include iterative development, adoption of use- case and scenario-based techniques and viewpoint- or stakeholder-based analysis; practices which require modelling and analysis in the presence of partial information about system behaviour.

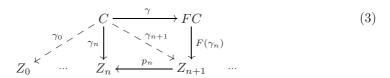

A workaround to the completeness assumption is to reinterpret the two sets of behaviours that a behaviour model describes. Rather than interpreting the behaviour that cannot be reproduced by the transitions of a model as proscribed behaviour, it can be interpreted as being "yet to be determined". This interpretation works for scenario-based specifications that have an existential semantics (e.g. MSCs [13]) as these specifications provide examples of what the system must do, but do not say anything about what it must not do. Consequently, a behaviour model synthesized from scenarios provides a lower bound from which to identify the behaviours that the system will provide but that have not been explicitly captured by the scenarios. As these new behaviours are identified, they are added to the scenario specification which is then used to synthesis a new behaviour model that includes these new behaviours. This elaboration process can be formalised at the behaviour level with some notion of refinements such as trace inclusion or simulation [20].

An alternative workaround is to consider the behaviour explicitly described by the transitions of a behaviour model as unclassified and to assume that the rest of the behaviour is known to be proscribed. This is the interpretation taken for senario-based specifications that have a universal semantics such as Constant LSCs [10]. In such approaches, as with approaches that do synthesis from declarative specifications such as goal models [19]. The specification prunes the acceptable space of behaviours as more universal properties are added to the specification. The fact that a behaviour satisfies a universal statement does not mean that the system is required to provide that trace; the trace could be

violating another property, possibly one yet to be elicited. Consequently, a behaviour model synthesized from properties should characterize all possible behaviours that do not violate the properties. Such a model provides an *upper bound* on all the behaviours that the system will actually provide, once implemented. Validation of behaviour models synthesized from properties can prompt the elicitation of more properties, which in turn will further approximate from above the intended behaviour of the system to be. In other words, as new properties are elicited, the resulting synthesized model will be able to do *less* (notion that can be formally captured using a traditional notion of refinement such as simulation), describing behaviour that is closer to that of the system to be.

The problem is that if behaviour models are to be synthesised from rich scenario based languages that use combine existential and universal scenarios as first envisioned in [10], the target synthesis formalism cannot be in the form of traditional behaviour models such as LTS because these are not capable of capturing simultaneously both the upper and lower bounds [22] that universal and existential statements provide.

#### 2 Partial Behaviour Models

Partial behaviour models, such as Modal Transition Systems (MTS) [17], disinguish between three kinds of behaviour, required, proscribed and unknown, and therefore can describe *both* an upper and a lower bound to the intended system behaviour, allowing both bounds to be refined simultaneously. For instance, MTS are equipped with two kinds of transitions required transitions and possible transitions. The former provide a lower bound to system behaviour, while the latter provide the lower bound to system behaviour.

The semantics of a partial behaviour model can be thought of as a set of traditional behaviour models. For instance, MTS semantics can be given in terms of sets of LTSs that provide all of the behaviour required by the MTS, do not provide any of the behaviour proscribed by the MTS, and make arbitrary decisions on the MTS's unknown behaviour. Intuitively, as more information becomes available, unknown or unclassified behaviour gets changed into either required or proscribed behaviour. The notion of refinement between MTSs capture this intuition formally and provides an elegant way of describing the process of behaviour model elaboration as one in which behaviour information is acquired and introduced into the behaviour model incrementally, gradually refining an MTS until it characterizes a single LTS.

The original notion of refinement was aimed at comparing MTS models with the same alphabet and no unobservable transitions and is referred to as strong refinement [17]. Although in [17] a notion of weak refinement that allows for unobservable actions was defined, this notion was then extended to account for models different alphabets [23]. More recently, an alternative, possibly more appropriate observational refinement, based on branching equivalence [25] has also been proposed [7].

A particularly useful notion in the context of software and requirements engineering is that of *merge*. Merging two consistent models is a process that should

result in a minimal common refinement of both models where *consistency* is defined as the existence of one common refinement. Intuitively, merging builds a model that characterises the intersection of the LTS characterised by the models being merged. In other words, the merge characterises the LTSs that provide all the required behaviour of the MTS being merged, and that do not provide any of the proscribed behaviour of the MTS being merged.

MTS merging can be used as the conjunction of multiple partial operational descriptions. The original formulation of was done by Larsen in [16] where an incomplete merge algorithm was proposed for MTS under strong refinement, recently we have presented a correct and complete version [8]. The problem of merge under observational refinements is still open, a partial result can be found in [23] where incomplete algorithm for merging models with different alphabets under weak refinement is presented.

We have revisted the problem of behaviour model synthesis in the context of MTS. We have provided a generic extension of synthesis approaches that start from existential scenario-based specifications and build LTS models [22]. The extension, produces an MTS model instead of an LTS which captures appropriately the lower bound to intended system behaviour provided by such specifications. However, given that MTS are more expressive than LTS, we have explored opportunities for the defining novel synthesis approaches that start from more expressive scenarios notations. In particular, we have investigated triggered existential scenarios [21] which have been neglected in existing scenario description languages as it is impossible to adequately capture their semantics using traditional behaviour models.

#### 3 Conclusions

In this talk we discuss Modal Transition Systems [17] and some of their theoretical foundations and semantics. We discuss how such models can support iterative and incremental behaviour modelling based on a notion of refinement that prunes the space of acceptable implementations of the system-to-be and based on model merging. We also discuss how merge and synthesis of Modal Transition Systems can aide in the analysis and elaboration of system behaviour from multiple, partial and heterogeneous descriptions of behaviour and demonstrate some of these ideas using the Modal Transition System Analyser, a tool that aims to support incremental elaboration of partial models [5] and that is available, open source, at http://sourceforge.net/projects/mtsa/. We finalise with a number of open problems and directions of future work.

# Acknowledgments

Dario Fischbein, Nicolas D'Ippolito, German Sibay, Greg Brunet, Mathieu Sassoulas, Victor Braberman, and Marsha Chechik have all collaborated on parts of the work we present. The work we present has been funded in part by CONICET and grant ERC 204853/PBM.

#### References

- Antonik, A., Huth, M., Larsen, K., Nyman, U., Wasowski, A.: EXPTIME-complete Decision Problems for Mixed and Modal Specifications. In: 15th International Workshop on Expressiveness in Concurrency (August 2008)

- Antonik, A., Huth, M., Larsen, K.G., Nyman, U., Wasowski, A.: Complexity of decision problems for mixed and modal specifications. In: Amadio, R.M. (ed.) FOSSACS 2008. LNCS, vol. 4962, pp. 112–126. Springer, Heidelberg (2008)

- Bontemps, Y., Heymans, P., Schobbens, P.-Y.: From live sequence charts to state machines and back: A guided tour. IEEE Transactions on Software Engineering 31(12), 999–1014 (2005)

- Brunet, G., Chechik, M., Uchitel, S.: Properties of behavioural model merging. In: Misra, J., Nipkow, T., Sekerinski, E. (eds.) FM 2006. LNCS, vol. 4085, pp. 98–114. Springer, Heidelberg (2006)

- 5. D'Ippolito, N., Fischbein, D., Chechik, M., Uchitel, S.: Mtsa: The modal transition system analyser. In: 23rd IEEE/ACM International Conference on Automated Software Engineering (ASE 2008), L'Aquila, Italy, September 15-19, pp. 475-476. IEEE, Los Alamitos (2008), http://sourceforge.net/projects/mtsa/

- Fantechi, A., Gnesi, S.: Formal modeling for product families engineering. In: Proceedings of Software Product Lines, 12th International Conference, SPLC 2008, Limerick, Ireland, September 8-12, pp. 193–202. IEEE Computer Society, Los Alamitos (2008)

- Fischbein, D., Braberman, V., Uchitel, S.: A sound observational semantics for modal transition systems. In: Leucker, M., Morgan, C. (eds.) ICTAC 2009. LNCS, vol. 5684, pp. 215–230. Springer, Heidelberg (2009)

- 8. Fischbein, D., Uchitel, S.: On correct and complete strong merging of partial behaviour models. In: Harrold, M.J., Murphy, G.C. (eds.) Proceedings of the 16th ACM SIGSOFT International Symposium on Foundations of Software Engineering, Atlanta, Georgia, USA, November 9-14, pp. 297–307. ACM, New York (2008)

- Fischbein, D., Uchitel, S., Braberman, V.A.: A foundation for behavioural conformance in software product line architectures. In: Hierons, R.M., Muccini, H. (eds.) ROSATEA, pp. 39–48. ACM, New York (2006)

- Harel, D., Marelly, R.: Come, Let's Play: Scenario-Based Programming Using LSCs and the Play-Engine. Springer, Heidelberg (2003)

- 11. Huth, M.: Refinement is complete for implementations. Formal Aspects of Computing 17(2), 113–137 (2005)

- 12. Hüttel, H., Larsen, K.G.: The use of static constructs in a modal process logic. In: Meyer, A.R., Taitslin, M.A. (eds.) Logic at Botik 1989. LNCS, vol. 363, pp. 163–180. Springer, Heidelberg (1989)

- 13. ITU. Recommendation z.120: Message sequence charts. ITU (2000)

- 14. Keller, R.M.: Formal verification of parallel programs. Commun. ACM (1976)

- Krka, I., Brun, Y., Edwards, G., Medvidovic, N.: Synthesizing partial component-level behavior models from system specifications. In: van Vliet, H., Issarny, V. (eds.) ESEC/SIGSOFT FSE, pp. 305–314. ACM, New York (2009)

- Larsen, K.G., Steffen, B., Weise, C.: A constraint oriented proof methodology based on modal transition systems. In: Brinksma, E., Steffen, B., Cleaveland, W.R., Larsen, K.G., Margaria, T. (eds.) TACAS 1995. LNCS, vol. 1019. Springer, Heidelberg (1995)

- 17. Larsen, K.G., Thomsen, B.: A modal process logic. In: Proceedings, Third Annual Symposium on Logic in Computer Science, Edinburgh, Scotland, UK, July 5-8. IEEE Computer Society, Los Alamitos (1988)

- 18. Larsen, K.G., Xinxin, L.: Equation solving using modal transition systems. In: Proceedings, Fifth Annual IEEE Symposium on Logic in Computer Science, Philadelphia, Pennsylvania, USA, June 4-7, pp. 108–117. IEEE Computer Society, Los Alamitos (1990)

- Letier, E., Kramer, J., Magee, J., Uchitel, S.: Deriving event-based transition systems from goal-oriented requirements models. Automated Software Engineering Journal 15(2), 175–206 (2008)

- 20. Milner, R.: Communication and Concurrency. Prentice-Hall, New York (1989)

- Sibay, G., Uchitel, S., Braberman, V.A.: Existential live sequence charts revisited. In: Schäfer, W., Dwyer, M.B., Gruhn, V. (eds.) 30th International Conference on Software Engineering (ICSE 2008), Leipzig, Germany, May 10-18, pp. 41-50. ACM, New York (2008)

- Uchitel, S., Brunet, G., Chechik, M.: Synthesis of partial behavior models from properties and scenarios. IEEE Transactions on Software Engineering 35(3), 384– 406 (2009)

- Uchitel, S., Chechik, M.: Merging partial behavioural models. In: Taylor, R.N., Dwyer, M.B. (eds.) Proceedings of the 12th ACM SIGSOFT International Symposium on Foundations of Software Engineering, Newport Beach, CA, USA, October 31 - November 6, pp. 43–52. ACM, New York (2004)

- Uchitel, S., Kramer, J., Magee, J.: Incremental Elaboration of Scenario-Based Specifications and Behaviour Models using Implied Scenarios. ACM TOSEM 13(1) (2004)

- van Gabbeek, R.J., Weijland, W.P.: Branching time and abstraction in bisimulation semantics. J. ACM 43(3), 555–600 (1996)

# Satisfiability Modulo Theories: An Appetizer

Leonardo de Moura and Nikolaj Bjørner

Microsoft Research, One Microsoft Way, Redmond, WA 98074, USA {leonardo,nbjorner}@microsoft.com

Abstract. Satisfiability Modulo Theories (SMT) is about checking the satisfiability of logical formulas over one or more theories. The problem draws on a combination of some of the most fundamental areas in computer science. It combines the problem of Boolean satisfiability with domains, such as, those studied in convex optimization and term-manipulating symbolic systems. It also draws on the most prolific problems in the past century of symbolic logic: the decision problem, completeness and incompleteness of logical theories, and finally complexity theory. The problem of modularly combining special purpose algorithms for each domain is as deep and intriguing as finding new algorithms that work particularly well in the context of a combination. SMT also enjoys a very useful role in software engineering. Modern software, hardware analysis and model-based tools are increasingly complex and multi-faceted software systems. However, at their core is invariably a component using symbolic logic for describing states and transformations between them. A well tuned SMT solver that takes into account the state-of-the-art breakthroughs usually scales orders of magnitude beyond custom ad-hoc solvers.

#### 1 Introduction

Satisfiability is one of the most fundamental problems in theoretical computer science, namely the problem of determining whether a formula expressing a constraint has a solution. Constraint satisfaction problems arise in many diverse areas including software and hardware verification, type inference, extended static checking, test-case generation, scheduling, planning, graph problems, among others [1]. The most well-known constraint satisfaction problem is propositional satisfiability SAT, where the goal is to decide whether a formula over Boolean variables, formed using logical connectives, can be made true by choosing true/ false values for its variables. Some problems require or are more naturally described in more expressive logics such as first-order logic. A first-order formula is formed using logical connectives, variables, quantifiers, function and predicate symbols. A solution, also known as a *model*, is an interpretation for the variable, function and predicate symbols that makes the formula true. Of particular recent interest is satisfiability modulo theories (SMT), where the interpretation of some symbols is constrained by a background theory. For example, the theory of arithmetic restricts the interpretation of symbols such as:  $+, \leq, 0$ , and 1.

SMT draws on the most prolific problems in the past century of symbolic logic: the decision problem, completeness and incompleteness of logical theories, and finally complexity theory. The computational complexity of most SMT problems is very high. The problem of modularly combining special purpose algorithms for each domain is as deep and intriguing as finding new algorithms that work particularly well in the context of a combination. The theory of linear arithmetic, which is the basis of linear programming, is one prominent theory that is useful in many applications. Linear programming algorithms can be used to check satisfiability of conjunctions of linear arithmetic inequalities, but they do not directly apply for Boolean combinations. SMT solvers distinguish themselves by handling such combinations.

It is well-known that SAT is NP-complete and first-order logic is undecidable. Due to this high computational complexity, it is infeasible to build a procedure that can solve arbitrary SMT problems. Therefore, most procedures focus on the more realistic goal of efficiently solving problems that occur in practice. They rely on the assumption that, although potentially big, most formulas produced by verification and analysis tools are *shallow*. That is, only a small fraction of a formula is really critical for establishing satisfiability. The rest consists of irrelevant noise.

In recent years, there has been an enormous progress in the scale of problems that can be solved, thanks to innovations in core algorithms, data structures, heuristics, and paying attention to implementation details. Modern SAT procedures can check formulas with hundreds of thousands variables and millions of clauses. A similar progress has being observed for SMT procedures for the more commonly occurring theories. The annual competition for SAT and SMT procedures is a key ingredient in driving progress [2]. In this paper, we provide a brief overview of SMT and the main technical ideas.

#### 1.1 An Example

We will introduce three theories used in SMT solvers using the following example:

$$b + 2 = c \land f(read(write(a, b, 3), c - 2)) \neq f(c - b + 1).$$

The formula uses the theory of arrays. It was introduced by McCarthy in [3] as part of forming a broader agenda for a calculus of computation. In the theory of arrays, there are two functions read and write. The term read(a, i) produces the value of array a at index i, while the term write(a, i, v) produces an array, which is equal to a except for possibly index i which maps to v. These properties can be summarized using the equations:

$$read(write(a, i, v), i) = v$$

$read(write(a, i, v), j) = read(a, j)$  for  $i \neq j$ .

They state that the result of reading write(a, i, v) at index j is v for i = j. Reading the array at any other index produces the same value as read(a, j). The formula also uses the function f, therefore for all t and s, if t = s, then f(t) = f(s)

(congruence rule). In other words, the only assumption about function f is that it always produce the same result when applied to the same arguments. The congruence rule implies that formulas remain equivalent when replacing equal terms. The example formula is unsatisfiable. That is, there is no assignment to the integers b and c and the array a such that the first equality b+2=c holds and at the same time the second disequality also is satisfied. One way of establishing the unsatisfiability is by replacing c by b+2 in the disequality, to obtain the equivalent

$$b+2=c \land f(read(write(a,b,3),b+2-2)) \neq f(b+2-b+1),$$

which after reduction using facts about arithmetic becomes

$$b+2=c \land f(read(write(a,b,3),b)) \neq f(3).$$

The theory of arrays implies that the nested array read/write functions reduce to 3 and the formula becomes:

$$b + 2 = c \wedge f(3) \neq f(3)$$

.

The congruence property of f entails that the disequality is false.

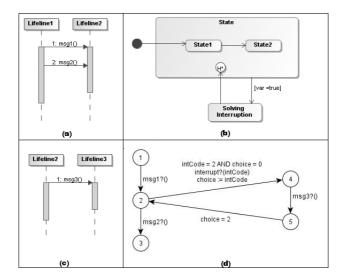

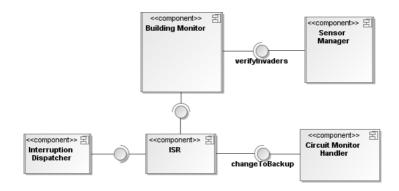

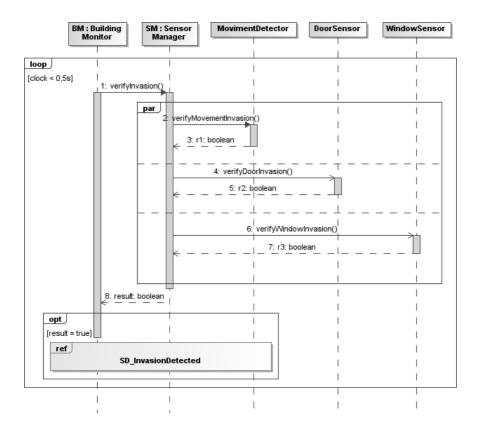

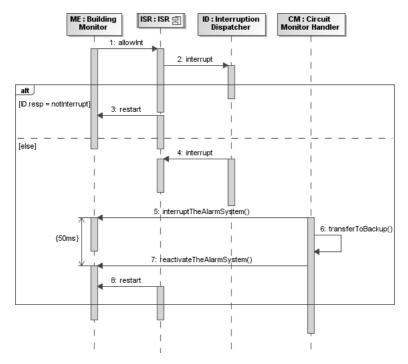

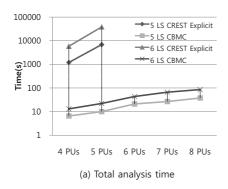

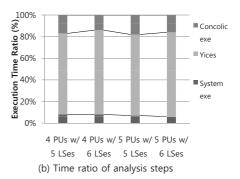

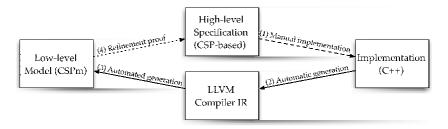

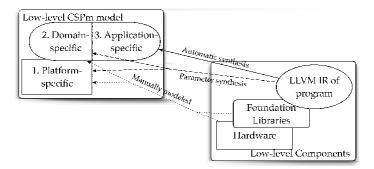

#### 2 Preliminaries